Electrum-100 Manual/User Interfaces, Connectors, and Jumpers

From Manuals

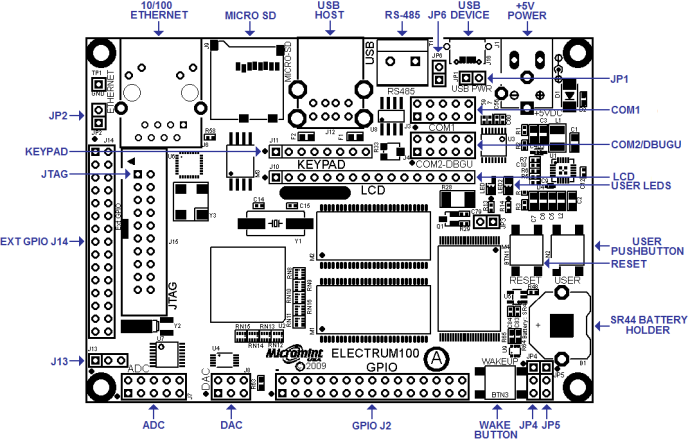

The following image shows where the connectors, headers, and jumpers are located on the Electrum 100.

Power Supply

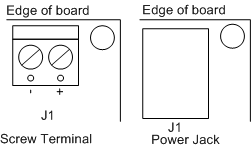

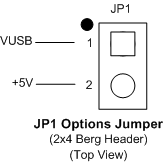

The Electrum 100 SBC requires a +5 VDC power supply on connector J1. Typical current requirements are 300 mA with all common peripherals enabled. When the LCD port is in use, the power supply must deliver 0.3V more than the voltage required for the LCD. This is to account for the voltage drop across the protection diode (D1). The LCD current requirements must be considered in sizing the power supply current capacity. J1 comes standard with a 2.5 mm positive center tapped female power supply jack. It can be populated with a 2 position screw terminal upon request. A diode (D1) will protect the Electrum 100 should polarity of the power supply be reversed. The board is also capable of being powered through the USB device port by putting a jumper on JP1.

WARNING: Power should not be connected to J1 and the user should make sure the board is not drawing too much power from the computers USB port.

10/100 Ethernet

The Electrum 100 is equipped with a fully-integrated 10/100 Mbps Ethernet port. The Media Access Control (MAC) is implemented in the AT91SAM9G20 and the Physical (PHY) layer is implemented with Micrel’s KSZ8041NL. J6 is the RJ-45 connector and it has integrated magnetics and LEDs completes the Ethernet sub-system. Please see the KSZ8041NL data sheet for further information on the PHY and the AT91SAM9G20 data sheet for the MAC.

USB Host

The AT91SAM9G20 has a fully-integrated USB v2.0 Dual Host port. The host port handles full-speed and low-speed protocols. The port reaches the outside world through J12. J12 is a Dual USB Type A connector. The USB host port controller is fully compliant with the OpenHCI specification. Please see the AT91SAM9G20 data sheet for further details on the USB Host port.

Serial (COM) Ports

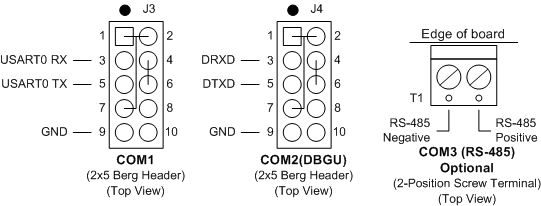

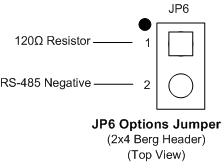

A Universal Synchronous Asynchronous Receivers/Transmitters (USART) is level shifted to RS-232 levels. USART0 (COM1) reaches the external world through a 2x5 pin berg header J3. The Universal Asynchronous Receiver/Transmitter (UART) Debug Unit (DBGU) is also level shifted to RS-232 levels. The DBGU (COM2/DBGU) reaches the external world through a 2x5 pin berg header J4. Please see figure 4.2 for the pin outs of COM1 and COM2/DBGU connectors. The two serial ports support software handshaking (XON/XOFF) and are considered to be Data Terminal Equipment(DTE). In order to communicate to a Personal Computer a null modem cable is required. To simplify interfacing to devices using hardware handshaking, a loopback is implemented on the modem control signals, from RTS to CTS and from DTR to CD and DSR. Note that the loopbacks do not provide flow control so software handshaking should be used when proper flow control is desired. The Electrum 100 has the option to be built with an RS-485 driver (U8). USART1 (COM3) reaches the external world through a two position screw terminal. Please see figure 4.2 for the pin out of COM3. The transmitter of the RS-485 driver is enabled by making port C bit 15 a logic 1. The RS-485 network can be terminated with a 120 ohm resistor by placing a jumper on JP3.

Micro-SD

The micro-SD socket (J9) enables micro-secure-digital memory cards to be plugged into the Electrum 100 microcontroller board. The micro-SD card allows the user the ability of a standard removable media for transferring data to and from the Electrum 100.

General Purpose Digital Inputs and Outputs

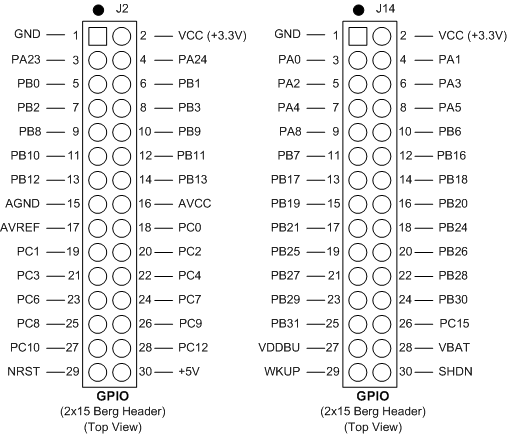

There are fifty-three total bits of GPIO available to the Electrum 100 user. Twenty-three are available on the J2 connector, twenty-four are available on J14 and 5 are available on J11 (optional keypad connector). Please see the pin out for J2 and J14 in Figure 4.3. For the pin out of J11 please see figure 4.4 in section 4.7.

Some of the GPIO on J2 and J14 have alternate functions other than digital inputs and outputs and are shared with some of the hardware on the board. Table 4.1 lists all of the alternate functions that are available to the Electrum 100 user and what connector they are available on. Table 4.2 lists the alternate functions, the hardware it is shared with, and a brief description of the alternate function for connector J2. Table 4.3 lists the alternate functions, the hardware it is shared with, and a brief description of the alternate function for connector J14. For further information on the alternate functions please refer to the AT91SAM9G20 data sheet.

| Alternate Function | Available on Connector |

|---|---|

| Programmable Clocks | J14 |

| External Interrupt 0 (IRQ0) | J2 |

| External Interrupt 1 (IRQ0) | J14 |

| Multimedia Card Slot B | J14 |

| USART0 Control Lines | J14, J11 |

| USART1 | J14 |

| USART2 | J2, J14 |

| USART3 | J2 |

| USART5 | J2 |

| Synchronous Serial Controller | J14 |

| Timer Counter 0 | J2, J11 |

| Timer Counter 1, 2 | J2, J14, J11, |

| Timer Counter 3, 4, and 5 | J2, J14 |

| Two-Wire Interface | J2 |

| Image Sensor | J2, J11, J14 |

| Analog to Digital Converter | J2 |

| J2 Pin# | Signal | Alternate Function | Notes | Shared Hardware |

|---|---|---|---|---|

| 1 | GND | Digital Ground | ||

| 2 | VCC | 3.3Volts DC | ||

| 3 | PA23 | TWD | Two-wire Data | |

| 4 | PA24 | TWCK | Two-wire Clock | |

| 5 | PB0 | SPI1_MISO/TIOA3 | SPI Channel 1 Master Input, Slave Output/Counter 3 I/O line A | Optional ADC, DAC |

| 6 | PB1 | SPI1_MOSI/TIOB3 | SPI Channel 1 Master Output, Slave Input/Counter 3 I/O line B | Optional ADC, DAC |

| 7 | PB2 | SPI1_SPCK/TIOA4 | SPI Channel 1 Clock/Timer Counter 4 I/O line A | Optional ADC, DAC |

| 8 | PB3 | SPI1_NPCS0/TIOA5 | SPI1 - Slave Select 0/Timer Counter 5 I/O line A | |

| 9 | PB8 | TXD2 | COM4 (USART2) TX | |

| 10 | PB9 | RXD2 | COM4 (USART2) RX | |

| 11 | PB10 | TXD3/ISI_D8 | COM5 (USART3) TX/Image Sensor DATA8 | |

| 12 | PB11 | RXD3/ISI_D9 | COM5 (USART3) RX/Image Sensor DATA9 | |

| 13 | PB12 | TXD5/ISI_D10 | COM6 (USART5) TX/Image Sensor DATA10 | Keypad (J11) |

| 14 | PB13 | RXD5/ISI_D11 | COM6 (USART5) RX/Image Sensor DATA11 | Keypad (J11) |

| 15 | AGND | Analog ground | ||

| 16 | AVCC | Analog power (3.3V) | ||

| 17 | AVREF | Analog Reference Voltage | ||

| 18 | PC0 | AD0/SCK3 | Analog Input 0/USART3 Serial Clock | |

| 19 | PC1 | AD1/PCK0 | Analog Input 1/Programmable Clock Output 0 | |

| 20 | PC2 | AD2/PCK1 | Analog Input 2/Programmable Clock Output 1 | |

| 21 | PC3 | AD3/SPI1_NPCS3 | Analog Input 3/ SPI1 - Slave Select 3 | DAC SYNC |

| 22 | PC4 | SPI1_NPCS2 | SPI1 - Slave Select 2 | ADC Chip Select |

| 23 | PC6 | TIOB2 | Timer Counter 2 I/O line B | LCD (J10) |

| 24 | PC7 | TIOB1 | Timer Counter 1 I/O line B | LCD (J10) |

| 25 | PC8 | RTS3 | USART3 Request to Send | LCD (J10) |

| 26 | PC9 | TIOB0 | Timer Counter 0 I/O line B | |

| 27 | PC10 | CTS3 | USART3 Clear to Send | LCD (J10) |

| 28 | PC12 | IRQ0 | External Interrupt 0 | |

| 29 | NRST | Microcontroller Reset | ||

| 30 | +5V | +5 Volts DC |

| J14 Pin# | Signal | Alternate Functions | Notes | Shared Hardware |

|---|---|---|---|---|

| 1 | GND | Digital Ground | ||

| 2 | VCC | 3.3Volts DC | ||

| 3 | PA0 | SPI0_MISO/ MCDB0 | SPI0 - Master In Slave Out/ Multimedia Card Slot B DATA0 | Data Flash |

| 4 | PA1 | SPI0_MOSI/ MCCDB | SPI0 - Master Out Slave In/ Multimedia Card Slot B Command | Data Flash |

| 5 | PA2 | SPI0_SPCK | SPI0 - Serial Clock | Data Flash |

| 6 | PA3 | SPI0_NPCS0/ MCDB3 | SPI0 - Slave Select 0/ Multimedia Card Slot B DATA3 | |

| 7 | PA4 | RTS2/ MCDB2 | USART2 Request to Send/ Multimedia Card Slot B DATA2 | |

| 8 | PA5 | CTS2/ MCDB1 | USART2 Clear to Send/ Multimedia Card Slot B DATA1 | |

| 9 | PA8 | MCCK | Multimedia Card Clock | microSD |

| 10 | PB6 | TXD1/TCLK1 | COM3 (USART1) TX/Timer 1 External Clock Input | Optional RS-485 |

| 11 | PB7 | RXD1/TCLK2 | COM3 (USART1) RX/Timer 2 External Clock Input | Optional RS-485 |

| 12 | PB16 | TK0/TCLK3 | SSC0 Transmitter Clock/Timer 3 External Clock Input | |

| 13 | PB17 | TF0/TCLK4 | SSC0 Transmitter Frame/Timer 4 External Clock Input | |

| 14 | PB18 | TD0/TIOB4 | SSC0 Transmitter Data/Timer Counter 4 I/O line B | |

| 15 | PB19 | RD0/TIOB5 | SSC0 Receiver Data/Timer Counter 5 I/O line B | |

| 16 | PB20 | RK0/ISI_D0 | SSC0 Receiver Clock/Image Sensor DATA0 | |

| 17 | PB21 | RF0/ISI_D1 | SSC0 Receiver Frame/Image Sensor DATA1 | |

| 18 | PB24 | DTR0/ ISI_D4 | USART0 Data Transmit Ready/Image Sensor DATA4 | LCD (J10) |

| 19 | PB25 | RI0/ ISI_D5 | USART0 Ring Indicator/Image Sensor DATA5 | LCD (J10) |

| 20 | PB26 | RTS0/ISI_D6 | USART0 Request to Send/Image Sensor DATA6 | LCD (J10) |

| 21 | PB27 | CTS0/ISI_D7 | USART0 Clear to Send/Image Sensor DATA7 | LCD (J10) |

| 22 | PB28 | RTS1/ISI_PCK | USART1 Request to Send/Image Sensor Data Clock | LCD (J10) |

| 23 | PB29 | CTS1/ISI_VSYNC | USART1 Clear to Send/Image Sensor Vertical Synchro | LCD (J10) |

| 24 | PB30 | PCK0/ISI_HSYNC | Programmable Clock Output 0/Image Sensor Horizontal Synchro | LCD (J10) |

| 25 | PB31 | PCK1/ISI_MCK | Programmable Clock Output 0/Image Sensor Reference Clock | LCD (J10) |

| 26 | PC15 | NWAIT/IRQ1 | External Wait Signal/External Interrupt Input | Optional RS-485 |

| 27 | VDDBU | Powers the Slow Clock oscillator | ||

| 28 | VBAT | Powers the Slow Clock oscillator through a 1.0V LDO | Battery Option | |

| 29 | WKUP | - | Wake-up Input | |

| 30 | SHDN | - | Shutdown Control |

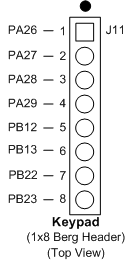

Keypad

A 4x4 matrix keypad using a 16-pin (2x8) ribbon cable can be connected to the microprocessor through J11. Please see Figure 4.4 for the pin out of the keypad connector. If the ports are not used for a keypad they may be used for their alternate functions. Table 4.4 lists the alternate functions for the 8-bits of I/O connected to J11.

| J11 Pin# | Signal | Alternate Functions | Notes | Shared Hardware |

|---|---|---|---|---|

| 1 | PA26 | TIOA0 | Timer Counter 0 I/O line A | |

| 2 | PA27 | TIOA1 | Timer Counter 1 I/O line A | |

| 3 | PA28 | TIOA2 | Timer Counter 2 I/O line A | |

| 4 | PA29 | SCK1 | USART1 Serial Clock | |

| 5 | PB12 | TXD5/ISI_D10 | COM6 (USART5) TX/Image Sensor DATA10 | J2 |

| 6 | PB13 | RXD5/ISI_D11 | COM6 (USART5) RX/Image Sensor DATA11 | J2 |

| 7 | PB22 | DSR0 /ISI_D2 | COM1 (USART0) Data Set Ready/ Image Sensor DATA2 | |

| 8 | PB23 | DCD0 /ISI_D3 | COM1 (USART0) Data Carrier Detect/ Image Sensor DATA3 |

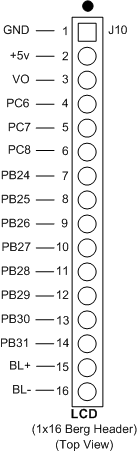

Liquid Crystal Display (LCD)

A standard alphanumeric LCD may be connected to J10 through a 32-pin (2x16) ribbon cable. The contrast for the LCD may be adjusted by turning potentiometer R33 located between J11 (Keypad) and J4 (COM2/DBGU). Please see figure 4.5 for the LCD’s connector pin out. If the LCD is not used then the GPIO may be used for their alternate functions and can be connected to via J2 and J14. Table 4.5 lists the alternate functions for the 8-bits of I/O connected to J11. AZ Displays ACM2004D series is recommended for use with the Electrum 100. http://www.azdisplays.com/index.php?id=Character_Modules&product=c2004d

| J10 Pin# | Signal | Alternate Functions | Notes | Shared Hardware |

|---|---|---|---|---|

| 1 | GND | Digital Ground | ||

| 2 | +5V | +5 Volts DC | ||

| 3 | VO | LCD Contrast | ||

| 4 | PC6 | TIOB2 | Timer Counter 2 I/O line B | J2 |

| 5 | PC7 | TIOB1 | Timer Counter 1 I/O line B | J2 |

| 6 | PC8 | RTS3 | USART3 Request to Send | J2 |

| 7 | PB24 | DTR0/ ISI_D4 | USART0 Data Transmit Ready/Image Sensor DATA4 | J14 |

| 8 | PB25 | RI0/ ISI_D5 | USART0 Ring Indicator/Image Sensor DATA5 | J14 |

| 9 | PB26 | RTS0/ISI_D6 | USART0 Request to Send/Image Sensor DATA6 | J14 |

| 10 | PB27 | CTS0/ISI_D7 | USART0 Clear to Send/Image Sensor DATA7 | J14 |

| 11 | PB28 | RTS1/ISI_PCK | USART1 Request to Send/Image Sensor Data Clock | J14 |

| 12 | PB29 | CTS1/ISI_VSYNC | USART1 Clear to Send/Image Sensor Vertical Synchro | J14 |

| 13 | PB30 | PCK0/ISI_HSYNC | Programmable Clock Output 0/Image Sensor Horizontal Synchro | J14 |

| 14 | PB31 | PCK1/ISI_MCK | Programmable Clock Output 0/Image Sensor Reference Clock | J14 |

| 15 | BL+ | LCD Backlight Anode | ||

| 16 | BL- | LCD Backlight Cathode |

JTAG

The JTAG port can be used for software download and debugging, reducing the need for an in-circuit emulator. For detailed information on the operation of the JTAG port with boundary scan, please refer to IEEE Standard 1149.1-Test Access Port and Boundary-Scan Architecture.

Pushbuttons and LED

The Electrum 100 comes standard with a user pushbutton, a reset push button, and two user LEDs. The user push button is connected to port A bit 31 with a 10kO pull-up resistor connected to it. User LED 1 is a yellow LED and is connected to port A bit 25. User LED 2 is a green LED and is connected to port A bit 30. Both LEDs can be illuminated by making the corresponding bit a logic low.

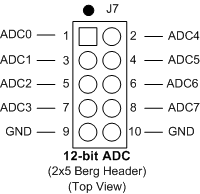

Optional Analog to Digital Converter (ADC)

The Electrum 100’s optional eight channels of 12-bit ADC can be connected to through J7. Please see figure 4.7 for the pin out of the ADC connector. The ADC is accessed through the AT91SAM9G20 SPI1 port. SPI1 slave select 2, port C bit 4, is the ADC’s chip select input for reading the conversion counts of the ADC.

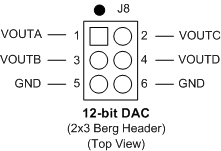

Optional Digital to Analog Converter (DAC)

The optional four channels of 12-bit DAC can be connected to through J8. Please refer to figure 4.8 for the pin out of the DAC connector. The DAC is accessed through the AT91SAM9G20 SPI1 port. SPI1 slave select 3, port C bit 3, is the DAC’s sync input for loading the conversion count into the DAC.

USB Device

The Electrum 100 comes equipped with a USB Device Port. The Device port is compliant with the USB V2.0 full-speed device specification. It reaches the outside world through J16. J16 is a micro USB Type AB connector. The USB device port has six endpoints that can be configured in one of several USB transfer types. Port C bit 5 is connected to the device ports VBUS power through a voltage divider. This allows the processor to detect when it is being used as a USB device. Please see the AT91SAM9G20 data sheet for further details on the USB Device port.

Option Jumpers

The Electrum 100’s option jumpers are used to enable memories and set-up power options. JP1 is used to power the Electrum 100 through the USB Device Port. WARNING: Power should not be connected to J1 and the user should make sure the board is not drawing too much power from the computers USB port. Figure 4.8 is the pin out for JP1.

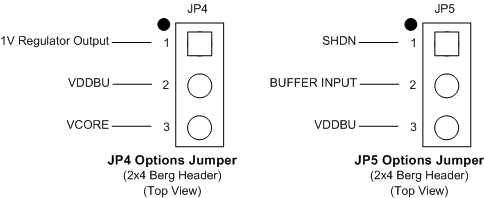

JP4 is used to determine how VDDBU is generated and is only populated if the battery option is present. When a jumper is installed on pins 1 and 2 of JP4, VDDBU is generated from VBAT and if the system loses power the shutdown controller will remain powered from the battery. VBAT can be applied on J14 pin 28 or from the SR44 battery holder. When JP4 is set to pins 2 and 3 VDDBU is generated by the VCORE switching regulator. Figure 4.9 contains the pin out for JP4.

JP5 is used to implement the SHDN pin for shutdown controller. When a jumper is installed on pins 1 and 2 of JP5, the SHDN pin controls the enable pin for the switching regulator. When JP4 is set to pins 2 and 3 of JP5 the outputs for the switching regulator is always enabled. Figure 4.9 contains the pon out for JP5.

JP6 is used to terminate the optional RS-485 network through a 120 resistor. Figure 4.10 is the pin out for JP6.

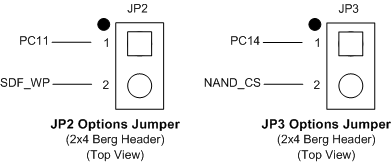

JP2 is used to connect the chip select signal to the serial dataflash. JP3 is used to connect the chip enable to the NAND Flash. Figure 4.11 contains the pin out of JP2 and JP3.

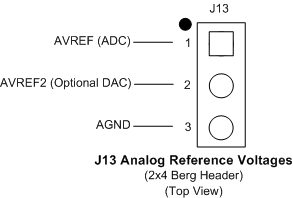

The analog reference voltages can be easily measured on J13. Figure 4.12 is the pin out for J13.